第四期 集成電路器件與設(shè)計(jì)的橋梁——深度解析集成電路設(shè)計(jì)

集成電路(IC)是現(xiàn)代電子技術(shù)的基石,從智能手機(jī)到超級(jí)計(jì)算機(jī),其身影無處不在。一枚功能強(qiáng)大的芯片并非憑空產(chǎn)生,它的誕生是精密器件物理與復(fù)雜系統(tǒng)設(shè)計(jì)完美融合的成果。本期將深入探討集成電路設(shè)計(jì)如何成為連接底層器件與頂層系統(tǒng)功能的至關(guān)重要的橋梁。

一、 基石:從器件物理到電路單元

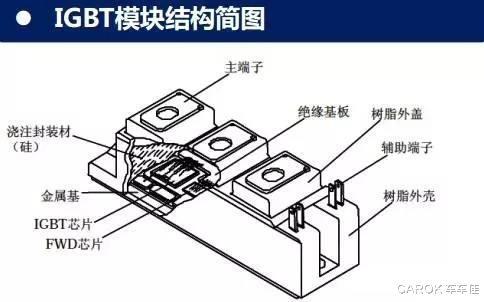

集成電路設(shè)計(jì)的起點(diǎn),是微觀世界的半導(dǎo)體器件,主要是晶體管(如當(dāng)今主流的FinFET或未來的GAA晶體管)。這些器件的物理特性——如開關(guān)速度、功耗、漏電流、驅(qū)動(dòng)能力、噪聲容限等——直接決定了電路最基本的性能邊界。設(shè)計(jì)工程師必須深刻理解這些特性:

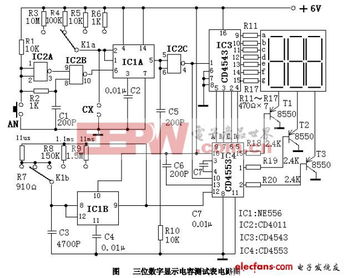

- 器件模型:基于物理方程和實(shí)驗(yàn)數(shù)據(jù)建立的數(shù)學(xué)模型,是設(shè)計(jì)工具(如SPICE)進(jìn)行電路仿真的基礎(chǔ)。模型精度直接關(guān)乎設(shè)計(jì)成敗。

- 工藝角(Process Corner):制造工藝的波動(dòng)會(huì)導(dǎo)致器件參數(shù)(如閾值電壓、載流子遷移率)在一定范圍內(nèi)變化。設(shè)計(jì)必須確保在所有可能的“角落”(如快-快、慢-慢、典型)下,電路功能都正確可靠。

- 寄生效應(yīng):隨著工藝節(jié)點(diǎn)進(jìn)入納米尺度,器件間的互連線產(chǎn)生的電阻、電容、電感等寄生參數(shù)影響日益顯著,甚至可能超過晶體管本身的影響,成為決定電路速度與功耗的關(guān)鍵。

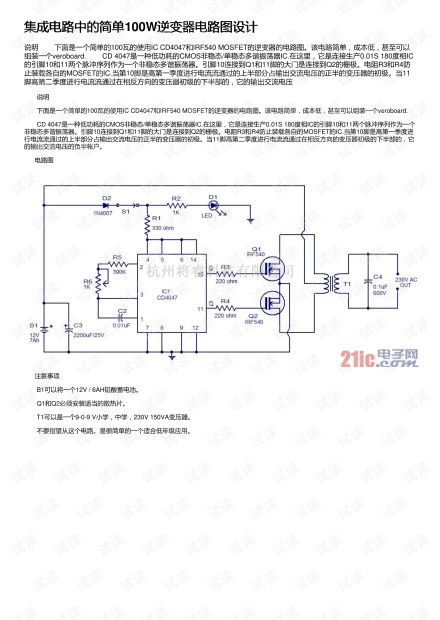

因此,設(shè)計(jì)的第一步,就是將抽象的器件物理參數(shù),轉(zhuǎn)化為邏輯門(如與非門、或非門)、存儲(chǔ)器單元、模擬模塊(如放大器、比較器)等可用的電路單元(標(biāo)準(zhǔn)單元庫)。這個(gè)單元庫是連接器件與復(fù)雜設(shè)計(jì)的預(yù)制構(gòu)件。

二、 核心:設(shè)計(jì)流程與層次化抽象

面對(duì)數(shù)十億甚至上百億個(gè)晶體管,直接進(jìn)行器件級(jí)設(shè)計(jì)是不可想象的。集成電路設(shè)計(jì)采用了經(jīng)典的層次化抽象和自動(dòng)化設(shè)計(jì)流程來駕馭這種復(fù)雜性。

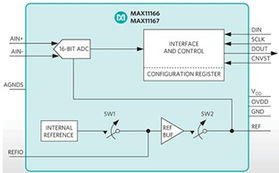

- 系統(tǒng)架構(gòu)與算法設(shè)計(jì):在最高抽象層,確定芯片的功能、性能指標(biāo)、功耗預(yù)算和成本目標(biāo)。對(duì)于數(shù)字系統(tǒng),可能涉及處理器架構(gòu)(如RISC-V)、AI加速器設(shè)計(jì);對(duì)于模擬/射頻系統(tǒng),則關(guān)乎信號(hào)鏈路的整體規(guī)劃。

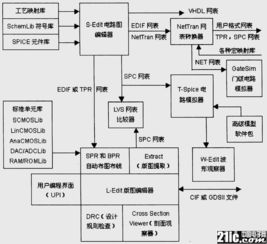

- 前端設(shè)計(jì)(邏輯設(shè)計(jì)):

- 硬件描述語言(HDL):使用Verilog或VHDL等語言,以寄存器傳輸級(jí)(RTL)描述芯片的行為和功能。這是將算法和架構(gòu)“翻譯”成硬件邏輯的關(guān)鍵步驟。

- 邏輯綜合:利用電子設(shè)計(jì)自動(dòng)化(EDA)工具,將RTL代碼、約束(如時(shí)序、面積)和標(biāo)準(zhǔn)單元庫作為輸入,自動(dòng)生成門級(jí)網(wǎng)表。這一過程將行為描述映射為具體的邏輯門電路連接。

- 驗(yàn)證:通過仿真、形式驗(yàn)證等方法,確保RTL設(shè)計(jì)的功能符合預(yù)期,是保證芯片“做對(duì)”的關(guān)鍵環(huán)節(jié)。

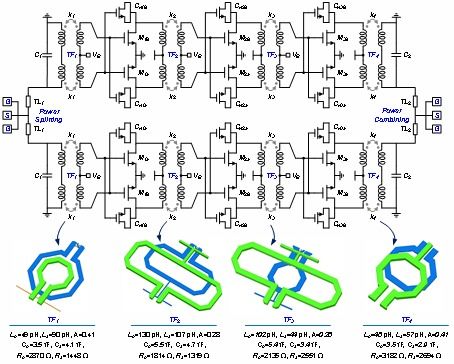

- 后端設(shè)計(jì)(物理設(shè)計(jì)):這是將邏輯網(wǎng)表“放置”到硅片上的過程,是橋梁中最貼近物理現(xiàn)實(shí)的一端。

- 布局規(guī)劃:規(guī)劃芯片核心、存儲(chǔ)器、接口等模塊的宏觀位置。

- 布局與布線(P&R):將每個(gè)邏輯門(標(biāo)準(zhǔn)單元)精確地放置在芯片版圖上,并用金屬線連接起來。此階段必須嚴(yán)格考慮時(shí)序、信號(hào)完整性、功耗、散熱和制造規(guī)則(DRC)。

- 時(shí)序收斂與簽核:通過靜態(tài)時(shí)序分析(STA)、功耗分析、物理驗(yàn)證等,確保設(shè)計(jì)在考慮所有寄生效應(yīng)和工藝變異后,仍能滿足所有性能、可靠性和可制造性要求。

三、 挑戰(zhàn)與趨勢(shì):橋梁的演進(jìn)

隨著摩爾定律逼近物理極限,這座“橋梁”正面臨前所未有的挑戰(zhàn),也在不斷進(jìn)化:

- 設(shè)計(jì)與工藝協(xié)同優(yōu)化(DTCO):設(shè)計(jì)不再被動(dòng)接受工藝提供的器件,而是與制造廠深度合作,針對(duì)特定設(shè)計(jì)優(yōu)化工藝模塊,或?yàn)樘囟üに嚬?jié)點(diǎn)定制設(shè)計(jì)方法,以挖掘每一代工藝的最大潛力。

- 系統(tǒng)與工藝協(xié)同優(yōu)化(STCO):在更高級(jí)別,將系統(tǒng)架構(gòu)(如存算一體、芯粒Chiplet)與先進(jìn)封裝(如2.5D/3D集成)和工藝技術(shù)結(jié)合考慮,從系統(tǒng)整體出發(fā)尋求最優(yōu)解。

- EDA與AI的融合:人工智能技術(shù)正在注入設(shè)計(jì)全流程,用于加速布局布線、優(yōu)化功耗、預(yù)測(cè)性能、甚至輔助架構(gòu)探索和代碼生成,以應(yīng)對(duì)日益增長(zhǎng)的設(shè)計(jì)復(fù)雜度和縮短上市時(shí)間。

- 異構(gòu)集成:將不同工藝節(jié)點(diǎn)、不同功能(數(shù)字、模擬、射頻、存儲(chǔ)、光電)的芯粒集成在一起,要求設(shè)計(jì)方法學(xué)從單一的“片上系統(tǒng)”(SoC)向“系統(tǒng)級(jí)封裝”(SiP)拓展,橋梁的連接范圍變得更為廣闊和立體。

###

集成電路設(shè)計(jì),本質(zhì)上是一門在多重約束下進(jìn)行創(chuàng)造性權(quán)衡的藝術(shù)與科學(xué)。它一端扎根于深?yuàn)W的半導(dǎo)體物理,另一端通向豐富多彩的應(yīng)用世界。這座“橋梁”的堅(jiān)固與高效,直接決定了芯片的性能、能效、成本和可靠性。隨著技術(shù)演進(jìn),這座橋梁不僅需要更加堅(jiān)固,還需要變得更加智能、靈活和立體,以承載未來信息社會(huì)對(duì)算力與智能日益增長(zhǎng)的渴望。理解設(shè)計(jì)與器件之間的深刻聯(lián)系,是叩開芯片世界大門的關(guān)鍵鑰匙。

如若轉(zhuǎn)載,請(qǐng)注明出處:http://m.yfl88.com/product/71.html

更新時(shí)間:2026-03-01 11:05:06