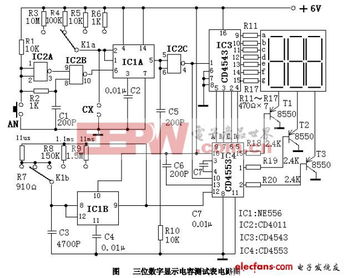

三位數(shù)字顯示電容測試表集成電路設(shè)計

引言

三位數(shù)字顯示電容測試表是一種用于精確測量電容值的電子儀器,其核心在于高性能的集成電路設(shè)計。該設(shè)計將模擬信號處理、數(shù)字邏輯控制與顯示驅(qū)動等功能集成于單一芯片,實現(xiàn)了小型化、高精度與低成本的目標。本文旨在闡述其核心電路的系統(tǒng)架構(gòu)、關(guān)鍵模塊設(shè)計及實現(xiàn)原理。

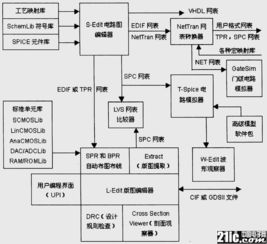

一、 系統(tǒng)總體架構(gòu)

整個電容測試表的集成電路采用混合信號設(shè)計,主要包含以下幾個核心模塊:

- 電容-頻率轉(zhuǎn)換電路(C-F轉(zhuǎn)換器):這是測量的核心。通常采用基于運算放大器的弛張振蕩器或多諧振蕩器電路。待測電容(Cx)作為定時元件接入振蕩回路,其容量值直接線性地決定輸出方波的頻率(Fx)。Cx越大,振蕩頻率Fx越低。

- 基準頻率發(fā)生器:提供一個高穩(wěn)定度的基準時鐘信號(Fref),用于在測量周期內(nèi)作為時間閘門或計數(shù)基準,其精度直接影響最終測量結(jié)果的準確性,通常由晶體振蕩器電路產(chǎn)生。

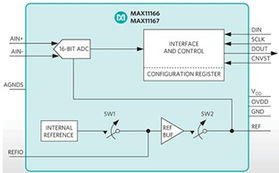

- 頻率-數(shù)字轉(zhuǎn)換與邏輯控制單元(主控制器):這是系統(tǒng)的數(shù)字大腦。在一個精確的基準時間門(例如由基準頻率分頻得到)內(nèi),對C-F轉(zhuǎn)換器輸出的頻率信號(Fx)進行計數(shù)。計數(shù)值N與電容值Cx成正比(N = k * Cx)。該單元還負責(zé)協(xié)調(diào)整個測量時序,如啟動測量、控制計數(shù)門、執(zhí)行運算和驅(qū)動顯示。

- 三位數(shù)字顯示驅(qū)動電路:將邏輯單元得到的二進制數(shù)值(對應(yīng)0-999)轉(zhuǎn)換為能夠驅(qū)動三位七段數(shù)碼管(LED或LCD)的信號。包括BCD碼轉(zhuǎn)換、掃描邏輯和段電流驅(qū)動電路。

- 量程自動切換與校準電路(高級功能):為覆蓋更寬的測量范圍(如幾pF到幾百μF),集成電路可集成量程判斷邏輯。通過切換與待測電容并聯(lián)或串聯(lián)的基準電阻/電容來改變C-F轉(zhuǎn)換器的量程,并由邏輯單元自動選擇并指示小數(shù)點位置。

二、 關(guān)鍵模塊設(shè)計詳解

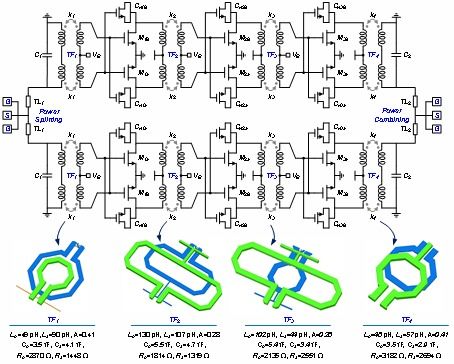

1. 電容-頻率轉(zhuǎn)換器(C-F Converter)

一種經(jīng)典設(shè)計是采用555定時器或?qū)S肅MOS振蕩器結(jié)構(gòu)。例如,使用一個雙比較器(施密特觸發(fā)器)和RS觸發(fā)器構(gòu)成弛張振蕩器。待測電容Cx通過一個恒流源進行充放電,其充放電的閾值電壓由內(nèi)部基準設(shè)定。電容電壓在高低閾值間線性變化,形成三角波,經(jīng)比較器輸出方波。頻率公式為:

Fx = K / (R * Cx)

其中K為常數(shù),R為精密基準電阻。通過選擇高穩(wěn)定度的基準電阻和低漂移的比較器,可以確保轉(zhuǎn)換的線性度和穩(wěn)定性。

2. 頻率-數(shù)字轉(zhuǎn)換與邏輯控制

此模塊通常以一個數(shù)字計數(shù)器為核心。其工作流程如下:

- 閘門時間生成:由基準頻率(如100kHz)通過分頻器產(chǎn)生一個精確的閘門時間T(例如100ms)。

- 信號計數(shù):在閘門時間T內(nèi),允許C-F轉(zhuǎn)換器輸出的脈沖信號通過一個與門,進入計數(shù)器進行計數(shù)。計數(shù)值 N = Fx * T。

- 運算與標定:由于N與Cx成反比(根據(jù)Fx公式),邏輯單元需執(zhí)行一次倒數(shù)運算(或直接在標定時調(diào)整線性化)。更常見的方法是在設(shè)計振蕩電路時,使頻率與電容成反比,然后通過硬件或固件進行線性化校正,最終得到與Cx成正比的數(shù)字量。

- 量程邏輯:若計數(shù)溢出或過小,則觸發(fā)量程切換電路,調(diào)整基準電阻R,并重新測量。同時控制顯示單元的小數(shù)點位置。

3. 顯示驅(qū)動電路

采用動態(tài)掃描驅(qū)動以節(jié)省引腳。邏輯控制單元將二進制結(jié)果轉(zhuǎn)換為三個BCD碼。顯示驅(qū)動電路包含:

- BCD-7段譯碼器:將每個位的BCD碼轉(zhuǎn)換為驅(qū)動七段數(shù)碼管各段的信號。

- 位掃描時序發(fā)生器:以較高頻率(如幾百Hz)循環(huán)激活三個位選通信號。

- 驅(qū)動級:提供足夠的電流(對于LED)或電壓(對于LCD)來點亮對應(yīng)的段。通常集成有恒流源或功率管。

三、 集成電路實現(xiàn)考量

- 工藝選擇:采用主流的CMOS工藝,兼顧模擬電路的精度和數(shù)字電路的密度與低功耗。

- 抗干擾設(shè)計:模擬部分(如振蕩器、比較器)與數(shù)字部分(計數(shù)器、邏輯)在版圖布局上需充分隔離,采用獨立的電源和地線(模擬VDD/AVDD,數(shù)字VDD/DVDD),防止數(shù)字開關(guān)噪聲干擾敏感的模擬信號。

- 精度保障:關(guān)鍵模擬元件(如振蕩器中的比較器、基準電流源)需精心設(shè)計,采用共源共柵結(jié)構(gòu)、差分對等以提高電源抑制比和溫度穩(wěn)定性。內(nèi)部基準電壓源/電流源的設(shè)計至關(guān)重要。

- 校準與測試:芯片需設(shè)計內(nèi)置自測試或校準模式,便于在生產(chǎn)中通過外部命令調(diào)整測量偏差,例如通過激光修調(diào)或數(shù)字微調(diào)(如熔絲或EEPROM)來校正基準。

四、

設(shè)計一款用于三位數(shù)字電容測試表的專用集成電路,是一項融合模擬與數(shù)字設(shè)計的系統(tǒng)工程。其性能核心在于高線性度、高穩(wěn)定性的電容-頻率轉(zhuǎn)換電路以及精確的時基控制。通過合理的系統(tǒng)架構(gòu)劃分、關(guān)鍵模塊的優(yōu)化設(shè)計以及嚴謹?shù)陌鎴D布局,可以在單顆芯片上實現(xiàn)高性能、低成本的電容測量方案,為便攜式、嵌入式電容測試儀表的發(fā)展提供可靠的核心部件。隨著工藝進步,未來此類芯片可集成更多智能功能,如自動歸零、溫度補償和通信接口等。

如若轉(zhuǎn)載,請注明出處:http://m.yfl88.com/product/72.html

更新時間:2026-03-01 16:17:07